分享文章

分享文章

酷睿Ultra 200V内核解密:四个E核略大于一个P核

声明:该文章来自(快科技)版权由原作者所有,K2OS渲染引擎提供网页加速服务。

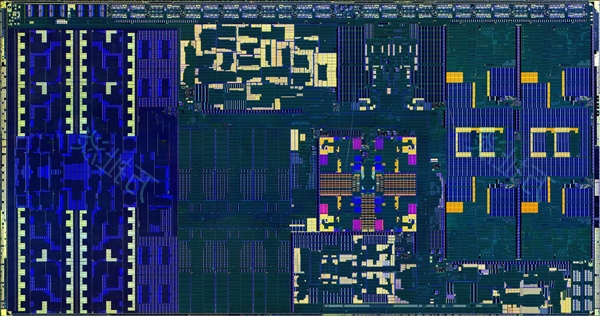

国外硬件专家Nemez利用B站网友“万扯淡”的底图,详细分析了Lunar Lake即酷睿Ultra 200V系列处理器的内部结构布局,其中大小核分布非常有意思。

酷睿Ultra 200V处理器分为计算模块、平台控制器模块,分别采用台积电3nm、6nm工艺,共同放置在台积电22nm制造的基底上。

计算模块面积为16.27×8.58=139.60平方毫米,平台控制器模块面积为11.51×3.97=45.69平方毫米,基底面积为16.77×13.10=219.69平方毫米。

每个核心自己有2.5MB二级缓存,也分成了两块。

旁边是四个为一组的Skymont架构的E核,集体共享12MB二级缓存,分成了三块。

对比来看,四个E核的面积稍微大于一个P核,这无疑是颇为值得称道的,因为上代四个E核面积约等于一个P核,而这一代E核的IPC性能整数提升了38%、浮点提升了68%,但面积却没有明显增大。

再往左是NPU AI引擎,分为六组NCE MAC阵列,每组猜测还是2MB缓存。

左侧边缘是GPU核显,一共八个Xe2 LPG架构的核心,以及分成两块的8MB二级缓存。

另外还有媒体引擎、显示引擎、8MB SLC系统缓存、128-bit LPDDR5X-8533内存控制器。

平台控制器模块内分布着PCIe 4.0/5.0控制器、雷电控制器、USB 3.x/2.0控制器、Wi-Fi与蓝牙控制器等。

平台控制器模块和和计算模块之间,通过两个模块桥接器(Tile Bridge)互相连接。

[超站]友情链接:

四季很好,只要有你,文娱排行榜:https://www.yaopaiming.com/

关注数据与安全,洞悉企业级服务市场:https://www.ijiandao.com/

- 1 中秘关于深化全面战略伙伴关系的声明 7904227

- 2 大爷要10元切糕结果切完变60元 7991154

- 3 教师指认猥亵现场坠亡 民警免予刑罚 7863544

- 4 秘鲁总统:已备美酒 欢迎光临! 7714049

- 5 外卖员吐槽尽量不要点黄焖鸡 7644043

- 6 俄媒:苏-57比中国歼-35更强 7597682

- 7 专家:本轮房价拐点全方位到来 7410828

- 8 俄罗斯开出停战先决条件 7395906

- 9 上海一路面的“操”字成网红打卡点 7295060

- 10 10月份主要经济指标回升明显 7181396

![滕文竹 是今日份的 大头贴[微风]#随手拍一夏##夏日颜艺大赏# ](https://imgs.knowsafe.com:8087/img/aideep/2021/11/22/a8aa369a967720d89f798a61bcc14af2.jpg?w=204)